Centre for Concurrent Computing

The two major projects within the Centre at RMIT were the:

- Parallel Systems Architecture Project (1987-1990)

- The Dataflow Project (1980-1987)

These projects were directed at the study of dataflow architectures arising from my PhD work at Manchester.

l-r John Feo (LLNL), Mark

Rawling, Neil Webb, Allan Young, Simon Wail, Greg Egan, Paul Whiting and Steve

Skedzlewski (LLNL)

David Abramson on Camera 1986

Funding for the Parallel Systems Architecture Project was due to Dr. Tommy Thomas, a member of the team that built the first stored program computer (Mark I) at Manchester, and the Foundation Director of the new CSIRO Division of Information Technology. Tommy knew that Australia was not producing enough PhDs in computer and engineering and science and seeded several projects around Australia. He was also responsible for David Abramson joining the Project. David had recently completed his PhD at Monash and worked with a will to writeup much of the latent and as yet unpublished research as I had until then enjoyed the doing more than the writing - to be truthful I still do.

FLO, was renamed CSIRAC II after the original CSIRAC. This naming occured when it became obvious to me that we would not complete the hardware prototype then well advanced. The widely held view by Australian funding bodies at the time, was that computer hardware development was best left to other countries, a view certainly not held by Tommy Thomas a farsighted friend.

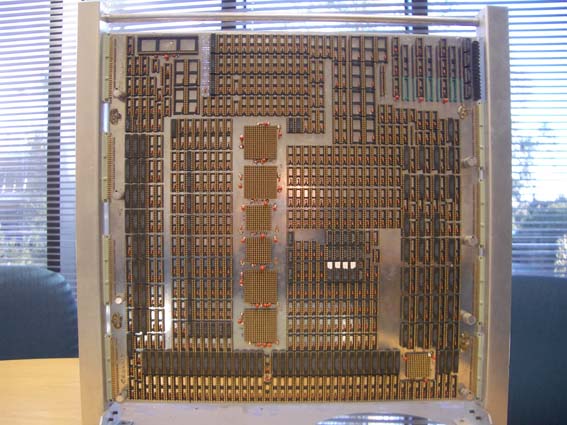

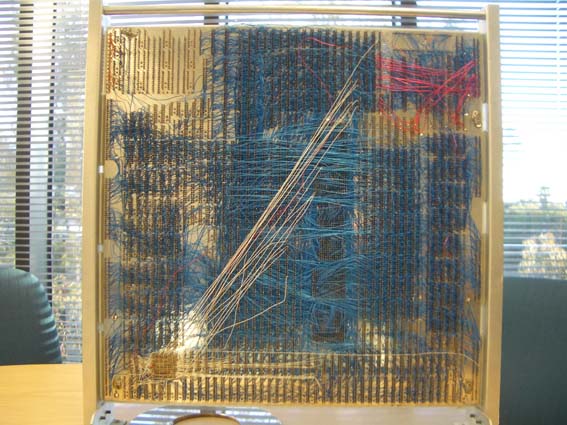

The partially commissioned Execution Unit of CSIRAC II

Languages

Compilers were developed for several languages. Pascal and IdA used used SISAL's IF1 as an intermediate compiler target allowing direct comparision between themselves and SISAL on all machines for which there was an IF1 backend - including CSIRAC II. By 1990 all compilers were fully operational and being used for applications studies and cross benchmarking.

- Whiting, P.G., and Pascoe, R.S.V., 'A History of Data-Flow Languages',

IEEE Annals of the History of Computing,

Volume 16 , Issue 4, p38 - 59, 1994.

Throughout the Project compiler development and application evaluation was performed by simulation. The simulator developed originally at Manchester over time became very comprehensive. It ran on all of our workstations and in a parallel implementation on a 20 processor Encore Multimax. It was the latter port which made it possible to run anything approximating real applications.

i2

i2 is a dataflow graph assembly language. It was written intially by myself and extend by Mark Rawling and Neil Webb to meet their requirements in the GHC and IF1 developments which targetted i2.

- Egan, G.K., Rawling, M.W., and Webb, N.J., 'i2: An Intermediate Language for the CSIRAC II Dataflow Computer' , Technical Report 31-002, Laboratory for Concurrent Computing Systems, School of Electrical Engineering, Swinburne Institute of Technology, Ver 2.0, Dec 1988.

DL1& DL2

The somewhat ostentatously named DL1 (Dataflow Language 1) was written to support Chris Richardson's research with me at Manchester. It was however one of the first operational compilers specifically for dataflow machines. Mark Rawling with Chris Richardson extended the language to DL2 adding iterators and other features.

- Rawling, M. and Richardson C.P., 'The RMIT Data Flow Computer DL1 User's Manual', Technical Report TR-112-059R, Department of Communication and Electronic Engineering, Royal Melbourne Institute of Technology, 1987.

- Egan, G.K., 'The RMIT Data Flow Computer: Intermediate Target Language', Technical Report TR-112-068 R, Department of Communication and Electronic Engineering', Royal Melbourne Institute of Technology, Jun. 1987.

IF1

Neil Webb was responsible for the IF1 to i2 backend. Like Mark Rawling's work on GHC this also led to fine tuning of the CSIRAC II instruction set.

- Webb, N.J., Whiting P.G. and Pascoe R.S.V., 'Implementing a Functional Language on the RMIT Dataflow Architecture', Technical Report TR-112-074R, Department of Communication and Electronic Engineering, Royal Melbourne Institute of Technology, 1988.

SISAL

A number of improvements were made to the SISAL implementation from LLNL and Colorado State. These were implemented on an Encore Multiprocessor donated to the Centre.

- Heath, W., 'The Implementation of Reduction Merge Operators in Sisal', Technical Report TR-112-079R, Department of Communication and Electronic Engineering, Royal Melbourne Institute of Technology, 1989.

- Abramson, D., Gaudiot J-L and Heath W., 'Parallel Manipulation of Arrays in SISAL', Technical Report TR-112-078R, Department of Communication and Electronic Engineering, Royal Melbourne Institute of Technology, 1988.

IdA (MIT Id)

IdA was Paul Whiting's implementation of the MIT Id language. It targetted IF1.

- Whiting, P.G., ' IDA: A Dataflow Programming Language', Technical Report TR-112-075R, Department of Communication and Electronic Engineering, Royal Melbourne Institute of Technology, 1988.

- Whiting, P.,'Compilation of a Functional Programming Language for the CSIRAC II Dataflow Computer', MAppSci, Department of Computer Science, Royal Melbourne Institute of Technology, 1991.

GHC (Guarded Horn Clauses)

In a somewhat bizzare competition Mark Rawling pitted his implementation of GHC against SISAL and IdA in numerical applications - and won from memory. The GHC work led to significant additions by me to CSIRAC IIs matching classes to support unification etc.

GHC unlike the IdA and Pascal compiler implementations targetted i2.

- Rawling, M. and Ramamohanarao K. 'GHC on the CSIRAC II Dataflow Computer, Technical Report TR-118-90R, Department of Communication and Electrical Engineering, Royal Melbourne Institute of Technology, 1989.

Pascal

The widely held view at the time was that dataflow machines could only be programmed using functional languages. This work showed this not to be the case. Pascal targetted an IF1 intermediate and could thus run on any processor for which there was a backend IF1 implementation.

- Wail, S.F., Implementing a conventional language for a dataflow architecture', Proceedings of the Third IEEE Symposium on Parallel and Distributed Processing, p164-171, Dallas Texas, 2-5 Dec, 1991.

- Wail, S., 'The Design and Implementation of a Conventional Language for the RMIT Dataflow Architecture, PhD, Department of Communication and Electrical Engineering, Royal Melbourne Institute of Technology, 1993.

Hardware

Emulator Prototype

The emulator followed the first 4 processor emulator developed at Manchester. Mark Rawling and Edward Zuk as my undergraduate students developed a Motorola M68K dual-processor prototype of a dataflow processing element. One M68K acted as the Matching Unit and the other as the Execution Unit. The emulator could also operate as a more conventional pipelined processor pair as required. Extensive use was made of hardware queues between processors as we knew that dataflow execution exhibited quite long runs of succesful then unsuccesful match sequences in the matching unit. There is some evidence that the Manchester Machine did not have sufficient queue space leading to alternatively execution unit starvation and matching unit stalls.

- Rawling, M.W. and Zuk E.A. , 'A Data-flow Processing Element', Design 3, Department of Communication and Electronic Engineering, Royal Melbourne Institute of Technology, Nov. 1982.

- Young, A., 'Data-flow Machine Hardware Documentation', Internal Documents, Department of Communication and Electronic Engineering, Royal Melbourne Institute of Technology, June 1984.

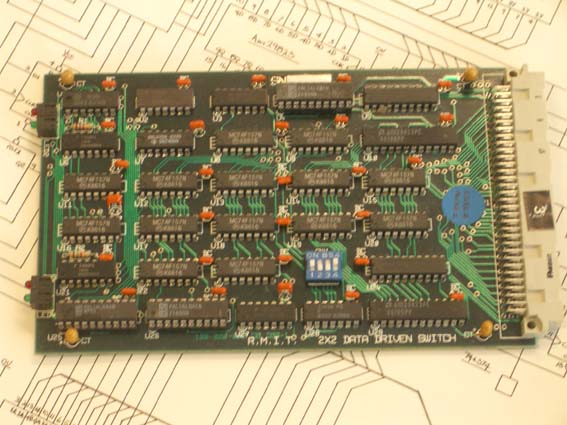

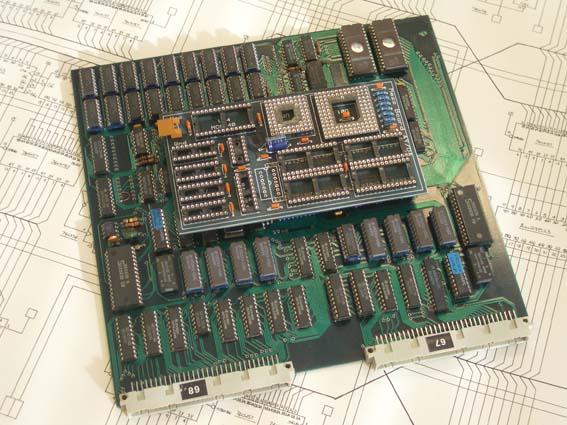

Dataflow Processor Prototype by Mark Rawling and Edward Zuk

Multiprocessor Dataflow Emulator

Allan Young, as part of his Master's, reimplemented the emulator of Mark Rawling and Edward Zuk. He was also responsible under my supervision for constructing the multistage network that connected the 32 Motorola 68K processors. At the time asynchornous design had slipped out of electrical engineering curricula but nonetheless the interconnection network was built and worked prompted in part by Professor Hiroaki Terada's work on clockless implementations of dataflow processors. Terada's logic was that if the mathematical formulation of dataflow has no time then the processors should not have clocks. Quotable quotes from Terada include "leave me alone I just want to build rice cookers" when confronted with a request to be involved in the 5th Generation Project. Those who know how complicated it is to cook rice perfectly will understand.

- Young, A., 'Data Driven Packet Switch Networks: A 2x2 Data Router', CH700 Research Methods, Department of Communication and Electronic Engineering, Royal Melbourne Institute of Technology, 1984.

- Young, A., 'Implementation of a Multistage Network for Interconnecting a Dataflow Multiprocessor', MEng, Department of Communication and Electronic Engineering, Royal Melbourne Institute of Technology, 1988.

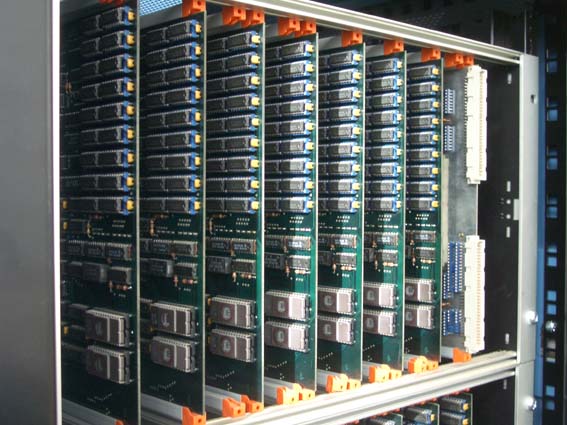

Sections of the multiprocessor emulator built by Allan Young - processor board shown with Motorola processor upgrade daughter board

CSIRAC II

- Egan, G.K., 'FLO: A Decentralised Data-flow System', Internal Report, Department of Computer Science, Victoria University of Manchester, Jan. 1979, revised Department of Communication and Electronic Engineering, Royal Melbourne Institute of Technology, Jan. 1983.

- Egan, G.K., 'The RMIT Data Flow Computer: Token and Node Definitions', Technical Report TR-112-060 R, Department of Communication and Electronic Engineering', Royal Melbourne Institute of Technology, June 1987, Original document Victoria University of Manchester, Oct. 1979.

- Abramson, D., Egan, G.K., Rawling, M., and Young, A., 'The RMIT Data Flow Computer: The Architecture', Technical Report TR-112-061 R, Department of Communication and Electronic Engineering, Royal Melbourne Institute of Technology, Melbourne, 1987.

- Abramson, D., Egan, G.K., Rawling, M., and Young, A., 'The RMIT Data Flow Computer: The Architecture', Technical Report TR-FA-87-02, Division of Information Technology, CSIRO, Sydney, Jan. 1987.

- Abramson, D.A., and Egan, G.K., 'An Overview of the RMIT/CSIRO Parallel Systems Architecture Project', Technical Report TR-112-065 R, Department of Communication and Electronic Engineering, Royal Melbourne Institute of Technology, Melbourne, Aug. 1987.

- M.L. Rawling, 'Implementation and Analysis of a Hybrid Dataflow System', MEng, Department of Communication and Electronic Engineering, Royal Melbourne Institute of Technology, 1988.

- M.L. Rawling, 'Implementation and Analysis of a Hybrid Dataflow System', Technical Report TR-118-094R, Department of Communication and Electronic Engineering, Royal Melbourne Institute of Technology, 1988.

- Abramson, D.A., and Egan, G.K., 'The RMIT/CSIRO Parallel Systems Architecture Project: Taking Australia into the 1990's and Beyond', Technical Report TR-112-076 R, Department of Communication and Electrical Engineering, Royal Melbourne Institute of Technology, Sep. 1988.

- Abramson, D.A., and Egan, G.K., 'The RMIT/CSIRO Parallel Systems Architecture Project: Taking Australia into the 1990's and Beyond', Technical Report TR-FA-88-02, Division of Information Technology, CSIRO, Sydney, Sept. 1988.

- Abramson, D.A., and Egan, G.K., 'Design Considerations for a High Performance Data Flow Multiprocessor', Technical Report TR-112-073 R, Department of Communication and Electrical Engineering', Royal Melbourne Institute of Technology, Aug. 1988.

- Abramson, D.A., and Egan, G.K., 'Design Considerations for a High Performance Data Flow Multiprocessor', Technical Report TR-FA-88-01, Division of Information Technology, CSIRO, Sydney, Aug. 1988.

Application Studies

- Egan, G.K., 'A Data-flow Computing System for Decentralised Control and Advanced Automata Applications', Proceedings of IREECON'81 International, Melbourne, Aug. 1981, p198-201.

- Richardson, C.P., and Egan, G.K., 'Object Recognition Using a Data-flow Computing System', EuroMicro Microprocessing and Microprogramming 7, North-Holland, p119-123, Feb. 1981.

- Egan, G.K., 'Simulation of Numerical Petri Nets Using Data-driven Computer Architectures', Reports 1, 2, 3 & 4, Telecom Contract 63228, Department of Communication and Electronic Engineering, Royal Melbourne Institute of Technology, 1983-84.

- Egan, G.K., and Richardson, C.P., 'Manipulator Control Using a Data-driven Multi-processor Computer System', National Conference and Exhibition on Robotics, Melbourne, Aug, 1984.

- Abramson, D., Egan, G.K., and Baharis, C., 'The RMIT Data Flow Computer: Benchmarks', Technical Report TR-112-058 R, Department of Communication and Electronic Engineering, Royal Melbourne Institute of Technology, Melbourne, Aug. 1987.

- Abramson, D., 'Using a Dataflow Multiprocessor for Functional Logic Simulation', Technical Report TR-112-063R, Department of Communication and Electronic Engineering, Royal Melbourne Institute of Technology, 1987.

- Abramson, D., 'Constructing School Timetables using Simulated Annealing: Sequential and Parallel Algorithms', Technical Report TR-112-069R, Department of Communication and Electronic Engineering, Royal Melbourne Institute of Technology, 1987.

- Abramson, D., 'A Language and Compiler System for Specifying Timetable Requirements', Technical Report TR-112-071R, Department of Communication and Electronic Engineering, Royal Melbourne Institute of Technology, 1988.

- Abramson, D.A., 'Case Studies in Parallel Processing', Technical Report TR-112-081R, Department of Communication and Electronic Engineering, Royal Melbourne Institute of Technology, 1989.

- Egan, G.K., Webb, N.J., and Bohm, A.P.W., 'Numerical Applications on the RMIT/CSIRO Dataflow Machine-CSIRAC II', Technical Report TR-118-082 R, Department of Communication and Electrical Engineering', Royal Melbourne Institute of Technology, Sep. 1988.

- Abramson, D.A., 'Directory of Parallel Computing Research Projects in Australia', Technical Report TR-118-085R, Department of Communication and Electronic Engineering, Royal Melbourne Institute of Technology, 1989.

- Egan, G.K., 'Parallel Computing: Easy as Pi, Technical Report TR-118-084 R, Department of Communication and Electrical Engineering, Royal Melbourne Institute of Technology, June 1989.

- Egan, G.K., 'Some Shallow Experiences: The Shallow Water Numerical Weather Prediction Program', Technical Report TR-118-086 R, Department of Communication and Electrical Engineering, Royal Melbourne Institute of Technology, Aug. 1989.

- Chang, P.S., and Egan, G.K., 'Performance Evaluation of a Parallel Implementation of a Spectral Barotropic Numerical Weather Prediction Model in the Functional Language SISAL', 2nd Australian Supercomputer Conference, Canberra, Dec, 1989.

- Chang, P.S., and Egan, G.K., 'A Parallel Implementation of the Barotropic Numerical Weather Prediction Model in the Functional Language SISAL', Technical Report TR-118-088 R, Department of Communication and Electrical Engineering, Royal Melbourne Institute of Technology, Aug. 1989.

- Chang, P.S., and Egan, G.K., 'Performance Evaluation of a Parallel Implementation of a Spectral Barotropic Numerical Weather Prediction Model in the Functional Language SISAL', Technical Report TR-118-91R, Department of Communication and Electrical Engineering, Royal Melbourne Institute of Technology, Oct. 1989.

- P.S. Chang, 'Implementation of a Numerical Weather Prediction Model in SISAL', MEng, Department of Communication and Electrical Engineering, Royal Melbourne Institute of Technology, 1990.

- C. Baharis, 'Tomographic Reconstruction on the CSIRAC II Dataflow Computer', MEng, Department of Communication and Electrical Engineering, Royal Melbourne Institute of Technology, 1991.

Associated Undergraduate Thesis Projects

Supervised by me:

- Biggs, I., 'An NMOS VLSI Queue for the Data-flow Multiprocessor', Design 3 Report, Department of Communication and Electronic Engineering, Royal Melbourne Institute of Technology, Nov. 1983.

- Siow, A., 'An NMOS VLSI Communication Switch for the Data-flow Multiprocessor, Design 3 Report, Department of Communication and Electronic Engineering, Royal Melbourne Institute of Technology, Nov. 1983.

- Walkington M., 'A Graphical Data-flow Compiler', Design 2 Report, Department of Communication and Electronic Engineering, Royal Melbourne Institute of Technology, Nov. 1983.

- Baharis C., 'Data-flow Machine Packet Communication System Switch I', Design 3 Report, Department of Communication and Electronic Engineering, Royal Melbourne Institute of Technology, Nov. 1984.

- Brennan, C., & Gallant, J., 'Robot Peripheral Processor', Department of Communication and Electronic Engineering, Royal Melbourne Institute of Technology, Nov. 1984.

- Calvert D., 'Data-flow Machine Packet Communication Switch (NMOS) III', Design 3 Report, Department of Communication and Electronic Engineering, Royal Melbourne Institute of Technology, Nov. 1984.

- Dalloste S., 'Data-flow Machine Packet Communication System Switch II', Design 3 Report, Department of Communication and Electronic Engineering, Royal Melbourne Institute of Technology, Nov. 1984.

- Chan S.K., and Lim K.K., 'Data-flow Machine Mathematics-Element', Design 3 Report, Department of Communication and Electronic Engineering, Royal Melbourne Institute of Technology, Nov. 1984.

- Gallant, J., Walkington, M., 'Optical Communications for Data-Flow', Design 3, Department of Communication and Electronic Engineering, Royal Melbourne Institute of Technology, Nov. 1984.

- Mogg, C.S., 'Robot Dataflow Compiler', Design 2 Project, Department of Communication and Electronic Engineering, Royal Melbourne Institute of Technology, Nov. 1984.

- Singh, D., 'Data-Flow Input/Output Processor', Department of Communication and Electronic Engineering, Royal Melbourne Institute of Technology, Nov. 1984.

- McGrath, P., 'Array Processor', Design 4, Department of Communication and Electronic Engineering, Royal Melbourne Institute of Technology, Nov. 1986.

People

- Greg Egan, Laboratory Director, CSIRAC II Architecture

- David Abramson, CSIRAC II Architecture

- Alan Young, Dataflow Emulator, Asynchronous MIN

- Mark Rawling, Dataflow Emulator, CSIRAC II Architecture, GHC Compiler

- Paul Whiting, IdA Compiler

- Simon Wail, Pascal Compiler

- Bob Pascoe, IdA Compiler

- Neil Webb, CSIRAC II IF1 Translator

- Rao, GHC Compiler

- Jacek Gibert, GHC Compiler

- Chris Baharis, Tomography

- Warwick Heath, Multiprocessor Tools, SISAL Optimisation techniques

- Pau Chang, Numerical Weather Prediction Codes in SISAL

- Ian Donaldson, Dataflow Emulator Operating Software, Systems Support

- Paul Beckett, Translation of SDL to IF1

- .....others to be added when/if I remember

Visitors

- Wim Bohm, Manchester University now Colorado State Fort Collins

- John Feo, 1986, Lawrence Livermore National Laboratory now San Diego Supercomputing Centre

- Steve Skedzlewski, 1986, Lawrence Livermore National Laboratory

- Jean-Luc Gaudiot, December 1988-February 1989, University of Southern California now Irvine

- Stephen Brobst, January 1989, MIT now TeraData

Research Associations & Collaborations

- Centre for Novel Computing, Computer Science, Victoria University of Manchester

- CSIRO

- Terada Laboratory, Osaka University

- Sisal Project, Lawrence Livermore National Laboratories

I left RMIT in 1990 to take up a position as Foundation Chair at Swinburne Institute of Technology where I formed the Laboratory for Concurrent Computing Systems and continued the dataflow research.